The execution of an arithmetic instruction may involve data transfer operations to position operands for input to the ALU, and to deliver the output of the ALU. Figure 3.5 illustrates the movements involved in both data transfer and arithmetic operations. In addition, of course, the ALU portion of the processor performs the desired operation.

# Logical

Most machines also provide a variety of operations for manipulating individual bits of a word or other addressable units, often referred to as "bit twiddling." They are based upon Boolean operations (see Appendix B).

Some of the basic logical operations that can be performed on Boolean or binary data are shown in Table 10.6. The NOT operation inverts a bit. AND, OR, and Exclusive-OR (XOR) are the most common logical functions with two operands. EQUAL is a useful binary test.

These logical operations can be applied bitwise to *n*-bit logical data units. Thus, if two registers contain the data

$$(R1) = 10100101$$

$(R2) = 00001111$

then

$$(R1) AND (R2) = 00000101$$

where the notation (X) means the contents of location X. Thus, the AND operation can be used as a mask that selects certain bits in a word and zeros out the remaining bits. As another example, if two registers contain

$$(R1) = 10100101$$

$(R2) = 11111111$

then

$$(R1) XOR (R2) = 01011010$$

With one word set to all 1s, the XOR operation inverts all of the bits in the other word (ones complement).

In addition to bitwise logical operations, most machines provide a variety of shifting and rotating functions. The most basic operations are illustrated in Figure 10.5. With a logical shift, the bits of a word are shifted left or right. On one end, the bit shifted out

Table 10.6 Basic Logical Operations

| -/P        | o o  | NOTE               | PANDO      | PORG | PXORG                          | P=Q · |

|------------|------|--------------------|------------|------|--------------------------------|-------|

| 0          | 0    | 1                  | 110 IO     | 0    | and a small of the safe of the |       |

| 0          | 12.5 | 1                  | A. 0.10.48 | 1 2  |                                | 0     |

| 1          | 0    | 0                  | 0          | 1    | and the book of the            | , 0   |

| 11/1/10/10 |      | March 1970 Comment | 1          |      | 0                              |       |

code in the sequence of the binary representation of the EBCDIC code; that is, the IRA code is placed in the table at the relative location equal to the binary value of the EBCDIC code of the same character. Thus, locations 10F0 through 10F9 will contain the values 30 through 39, because F0 is the EBCDIC code for the digit 0, and 30 is the IRA code for the digit 0, and so on through digit 9. Now suppose we have the EBCDIC for the digits 1984 starting at location 2100 and we wish to translate to IRA. Assume the following:

- Locations 2100-2103 contain F1 F9 F8 F4.

- R1 contains 2100.

- R2 contains 1000.

Then, if we execute

TR R1, R2, 4

locations 2100-2103 will contain 31 39 38 34.

# Input/Output

Input/output instructions were discussed in some detail in Chapter 7. As we saw, there are a variety of approaches taken, including isolated programmed I/O, memorymapped programmed I/O, DMA, and the use of an I/O processor. Many implementations provide only a few I/O instructions, with the specific actions specified by parameters, codes, or command words.

# **System Control**

System control instructions are those that can be executed only while the processor is in a certain privileged state or is executing a program in a special privileged area of memory. Typically, these instructions are reserved for the use of the operating system.

Some examples of system control operations are as follows. A system control instruction may read or alter a control register; we discuss control registers in Chapter 12. Another example is an instruction to read or modify a storage protection key, such as is used in the S/390 memory system. Another example is access to process control blocks in a multiprogramming system.

#### Transfer of Control

For all of the operation types discussed so far, the next instruction to be performed is the one that immediately follows, in memory, the current instruction. However, a significant fraction of the instructions in any program have as their function changing the sequence of instruction execution. For these instructions, the operation performed by the processor is to update the program counter to contain the address of some instruction in memory.

There are a number of reasons why transfer-of-control operations are required. Among the most important are the following:

1. In the practical use of computers, it is essential to be able to execute each instruction more than once and perhaps many thousands of times. It may require thousands or perhaps millions of instructions to implement an application. This

would be unthinkable if each instruction had to be written out separately. If a table or a list of items is to be processed, a program loop is needed. One sequence of instructions is executed repeatedly to process all the data.

- 2. Virtually all programs involve some decision making. We would like the computer to do one thing if one condition holds, and another thing if another condition holds. For example, a sequence of instructions computes the square root of a number. At the start of the sequence, the sign of the number is tested. If the number is negative, the computation is not performed, but an error condition is reported.

- 3. To compose correctly a large or even medium-size computer program is an exceedingly difficult task. It helps if there are mechanisms for breaking the task up into smaller pieces that can be worked on one at a time.

We now turn to a discussion of the most common transfer-of-control operations found in instruction sets: branch, skip, and procedure call.

Branch Instructions A branch instruction, also called a jump instruction, has as one of its operands the address of the next instruction to be executed. Most often, the instruction is a conditional branch instruction. That is, the branch is made (update program counter to equal address specified in operand) only if a certain condition is met. Otherwise, the next instruction in sequence is executed (increment program counter as usual). A branch instruction in which the branch is always taken is an unconditional branch.

There are two common ways of generating the condition to be tested in a conditional branch instruction. First, most machines provide a 1-bit or multiple-bit condition code that is set as the result of some operations. This code can be thought of as a short user-visible register. As an example, an arithmetic operation (ADD, SUBTRACT, and so on) could set a 2-bit condition code with one of the following four values: 0, positive, negative, overflow. On such a machine, there could be four different conditional branch instructions:

BRP X Branch to location X if result is positive.

BRN X Branch to location X if result is negative.

BRZ X Branch to location X if result is zero.

BRO X Branch to location X if overflow occurs.

In all of these cases, the result referred to is the result of the most recent operation that set the condition code.

Another approach that can be used with a three-address instruction format is to perform a comparison and specify a branch in the same instruction. For example,

BRE R1, R2, X Branch to X if contents of R1 = contents of R2.

Figure 10.6 shows examples of these operations. Note that a branch can be either forward (an instruction with a higher address) or backward (lower address). The example shows how an unconditional and a conditional branch can be used to create a repeating loop of instructions. The instructions in locations 202 through 210 will be executed repeatedly until the result of subtracting Y from X is 0.

Because we would like to be able to call a procedure from a variety of points, the processor must somehow save the return address so that the return can take place appropriately. There are three common places for storing the return address:

- Register

- Start of called procedure

- Top of stack

Consider a machine-language instruction CALL X, which stands for call procedure at location X. If the register approach is used, CALL X causes the following actions:

$$RN \longleftarrow PC + \Delta$$

$PC \longleftarrow X$

where RN is a register that is always used for this purpose, PC is the program counter, and  $\Delta$  is the instruction length. The called procedure can now save the contents of RN to be used for the later return.

A second possibility is to store the return address at the start of the procedure. In this case, CALL X causes

$$X \longleftarrow PC + \Delta$$

$PC \longleftarrow X + 1$

This is quite handy. The return address has been stored safely away.

Both of the preceding approaches work and have been used. The only limitation of these approaches is that they prevent the use of reentrant procedures. A reentrant procedure is one in which it is possible to have several calls open to it at the same time. A recursive procedure (one that calls itself) is an example of the use of this feature.

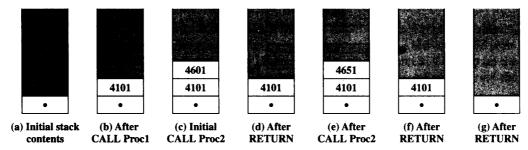

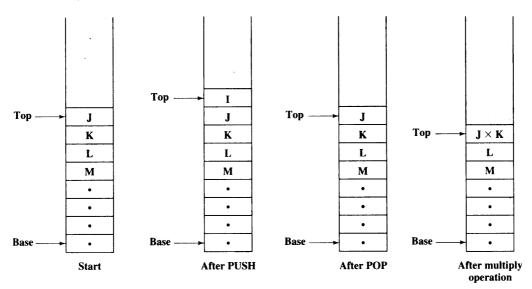

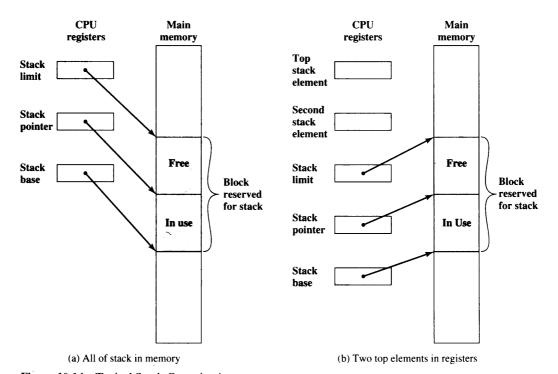

A more general and powerful approach is to use a stack (see Appendix 10A for a discussion of stacks). When the processor executes a call, it places the return address on the stack. When it executes a return, it uses the address on the stack. Figure 10.8 illustrates the use of the stack.

In addition to providing a return address, it is also often necessary to pass parameters with a procedure call. These can be passed in registers. Another possibility is to store the parameters in memory just after the CALL instruction. In this case, the return must be to the location following the parameters. Again, both of these approaches have drawbacks. If registers are used, the called program and the calling program must be written to assure that the registers are used properly. The storing of

Figure 10.8 Use of Stock to Implement Nested Subroutines of Figure 10.7

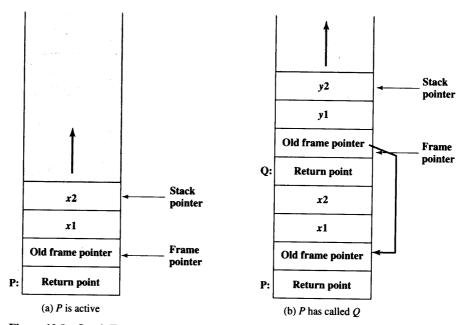

Figure 10.9 Stock Frame Growth Using Sample Procedures P and Q

parameters in memory makes it difficult to exchange a variable number of parameters. Both approaches prevent the use of reentrant procedures.

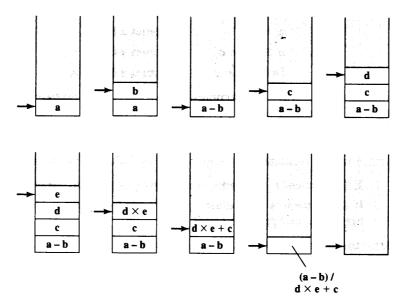

A more flexible approach to parameter passing is the stack. When the processor executes a call, it not only stacks the return address, it stacks parameters to be passed to the called procedure. The called procedure can access the parameters from the stack. Upon return, return parameters can also be placed on the stack. The entire set of parameters, including return address, that is stored for a procedure invocation is referred to as a stack frame.

An example is provided in Figure 10.9. The example refers to procedure P in which the local variables x1 and x2 are declared, and procedure Q, which P can call and in which the local variables y1 and y2 are declared. In this figure, the return point for each procedure is the first item stored in the corresponding stack frame. Next is stored a pointer to the beginning of the previous frame. This is needed if the number or length of parameters to be stacked is variable.

# 10.5 PENTIUM AND POWERPC OPERATION TYPES

# **Pentium Operation Types**

The Pentium provides a complex array of operation types, including a number of specialized instructions. The intent was to provide tools for the compiler writer to produce optimized machine language translation of high-level language programs. Table 10.8 lists the types and gives examples of each. Most of these are the conventional instructions found in most machine instruction sets, but several types of instructions are tailored to the 80x86/Pentium architecture and are of particular interest.

#### Call/Return Instructions

The Pentium provides four instructions to support procedure call/return: CALL, ENTER, LEAVE, RETURN. It will be instructive to look at the support provided by these instructions. Recall from Figure 10.9 that a common means of implementing the procedure call/return mechanism is via the use of stack frames. When a new procedure is called, the following must be performed upon entry to the new procedure:

- Push the return point on the stack.

- Push the current frame pointer on the stack.

- Copy the stack pointer as the new value of the frame pointer.

- Adjust the stack pointer to allocate a frame.

The CALL instruction pushes the current instruction pointer value onto the stack and causes a jump to the entry point of the procedure by placing the address of the entry point in the instruction pointer. In the 8088 and 8086 machines, the typical procedure began with the sequence

> **PUSH EBP** MOV EBP. ESP **SUB** ESP, space\_for\_locals

where EBP is the frame pointer and ESP is the stack pointer. In the 80286 and later machines, the ENTER instruction performs all the aforementioned operations in a single instruction.

The ENTER instruction was added to the instruction set to provide direct support for the compiler. The instruction also includes a feature for support of what are called nested procedures in languages such as Pascal, COBOL, and Ada (not found in C or FORTRAN). It turns out that there are better ways of handling nested procedure calls for these languages. Furthermore, although the ENTER instruction saves a few bytes of memory compared with the PUSH, MOV, SUB sequence (4 bytes versus 6 bytes), it actually takes longer to execute (10 clock cycles versus 6 clock cycles). Thus, although it may have seemed a good idea to the instruction set designers to add this feature, it complicates the implementation of the processor while providing little or no benefit. We will see that, in contrast, a RISC approach to processor design would avoid complex instructions such as ENTER and might produce a more efficient implementation with a sequence of simpler instructions.

Memory Management Another set of specialized instructions deals with memory segmentation. These are privileged instructions that can only be executed from the operating system. They allow local and global segment tables (called descriptor tables) to be loaded and read, and for the privilege level of a segment to be checked and altered.

The special instructions for dealing with the on-chip cache were discussed in Chapter 4.

Condition Codes We have mentioned that condition codes are bits in special registers that may be set by certain operations and used in conditional branch instructions. These conditions are set by arithmetic and compare operations. The compare

Table 10.9 Pentium Condition Codes

| Status Bit                                                                | Name                 | Description Description                                                                                                                                      |

|---------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lika k <b>o</b> li de Mare<br>1915 - Sala Salajas<br>20 - Gelesta Salajas | Carry see to gent Zi | Indicates carrying or borrowing into the left-most bif position following an arithmetic operation. Also modified by some of the shift and rotate operations. |

|                                                                           | Parity               | Parity of the result of an arithmetic or logic operation.  1 indicates even parity; 0 indicates odd parity.                                                  |

|                                                                           | Auxiliary Carry      | Represents carrying or borrowing between half-bytes of an 8-bit arithmetic or logic operation using the AL register.                                         |

| Z                                                                         | Zero                 | Indicates that the result of an arithmetic or logic operation is 0.                                                                                          |

| <b></b>                                                                   | Sign                 | Indicates the sign of the result of an arithmetic or logic operation.                                                                                        |

| 0                                                                         | Overflow             | Indicates an arithmetic overflow after an addition or subtraction.                                                                                           |

operation in most languages subtracts two operands, as does a subtract operation. The difference is that a compare operation only sets condition codes, whereas a subtract operation also stores the result of the subtraction in the destination operand.

Table 10.9 lists the condition codes used on the Pentium. Each condition, or combinations of these conditions, can be tested for a conditional jump. Table 10.10

Table 10.10 Pentium Conditions for Conditional Jump and SETcc Instructions

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Condition Tested                                                                          | Comment                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| A,NBE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C=0 AND Z=0                                                                               | Above; Not below or equal (greater than, unsigned)                     |

| AE, NB, NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g <b>C+0</b> g ngapagan ayan pertabah 140 m<br>Saka Padesa ayab Balas bahas bahas bahas b | Above or equal; Not below (greater than or equal, unsigned); Not carry |

| B, NAE, C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OCAL mangunga nahura belesar kelender<br>Konsak asak kecamatan berahan bahur              | Below; Not above or equal (less than, unsigned); Carry set             |

| BE, NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C=1 OR Z=1                                                                                | Below or equal; Not above (less than or equal, unsigned)               |

| E,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>Z=1</b>                                                                                | Equal; Zero (signed or unsigned)                                       |

| G, NLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | [(S=1 AND O=1) OR (S=0<br>and O=0)] AND [Z=0]                                             | Greater than; Not less than or equal (signed)                          |

| GE,NL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (S=1 AND O=1) OR (S=0<br>AND O=0)                                                         | Greater than or equal; Not less than (signed)                          |

| L,NGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (S=1 AND O=0) OR (S=0<br>AND O=1)                                                         | Less than; Not greater than or equal (signed)                          |

| LE, NG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (S=1 AND O=0) OR (S=0<br>AND O=1) OR (Z=1)                                                | Less than or equal; Not greater than (signed)                          |

| NE, NZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z=0                                                                                       | Not equal; Not zero (signed or unsigned)                               |

| <b>NO</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                           | No overflow                                                            |

| NS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S=0                                                                                       | Not sign (not negative)                                                |

| NP, PO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P=0                                                                                       | Not parity; Parity odd                                                 |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | O=1                                                                                       | Overflow                                                               |

| Prince of the state of the stat | P=1; Out along the term of the desirable or to                                            | Parity, Parity even                                                    |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>S=</b> I                                                                               | Sign (negative)                                                        |

shows the combinations of conditions for which conditional jump opcodes have been defined.

Several interesting observations can be made about this list. First, we may wish to test two operands to determine if one number is bigger than another. But this will depend on whether the numbers are signed or unsigned. For example, the 8-bit number 11111111 is bigger than 00000000 if the two numbers are interpreted as unsigned integers (255 > 0) but is less if they are considered as 8-bit two complement numbers (-1 < 0). Many assembly languages therefore introduce two sets of terms to distinguish the two cases: If we are comparing two numbers as signed integers, we use the terms less than and greater than; if we are comparing them as unsigned integers, we use the terms below and above.

A second observation concerns the complexity of comparing signed integers. A signed result is greater than or equal to zero if (1) the sign bit is zero and there is no overflow (S = 0 AND O = 0), or (2) the sign bit is one and there is an overflow. A study of Figure 9.4 should convince you that the conditions tested for the various signed operations are appropriate (see Problem 10.13).

Pentium MMX Instructions In 1996, Intel introduced MMX technology into its Pentium product line. MMX is set of highly optimized instructions for multimedia tasks. There are 57 new instructions that treat data in a SIMD (singleinstruction, multiple-data) fashion, which makes it possible to perform the same operation, such as addition or multiplication, on multiple data elements at once. Each instruction typically takes a single clock cycle to execute. For the proper application, these fast parallel operations can yield a speedup of two to eight times over comparable algorithms that do not use the MMX instructions [ATKI96].

The focus of MMX is multimedia programming. Video and audio data are typically composed of large arrays of small data types, such as 8 or 16 bits, whereas conventional instructions are tailored to operate on 32- or 64-bit data. Here are some examples: In graphics and video, a single scene consists of an array of pixels,<sup>2</sup> and there are 8 bits for each pixel or 8 bits for each pixel color component (red, green, blue). Typical audio samples are quantized using 16 bits. For some 3D graphics algorithms, 32 bits are common for basic data types. To provide for parallel operation on these data lengths, three new data types are defined in MMX. Each data type is 64 bits in length and consists of multiple smaller data fields, each of which holds a fixed-point integer. The types are as follows:

- Packet byte: Eight bytes packed into one 64-bit quantity

- Packed word: Four 16-bit words packed into 64 bits

- Packed doubleword: Two 32-bit doublewords packed into 64 bits

Table 10.11 lists the MMX instruction set. Most of the instructions involve parallel operation on bytes, words, or doublewords. For example, the PSLLW

<sup>&</sup>lt;sup>2</sup>A pixel, or picture element, is the smallest element of a digital image that can be assigned a gray level. Equivalently, a pixel is an individual dot in a dot-matrix representation of a picture.

Table 10.11 MMX Instruction Set

| Category                          | Instruction             | Description                                                                                                                   |  |

|-----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| i edding is jak<br>Sinaan Dag jak | PADD [B, W, D]          | Parallel add of packed eight bytes, four 16-bit words, or two 32-bit doublewords, with wraparound.                            |  |

|                                   | PADDS [B, W]            | Add with saturation.                                                                                                          |  |

|                                   | PADDUS [B, W]           | Add unsigned with saturation.                                                                                                 |  |

|                                   | PSUB [B, W, D]          | Subtract with wraparound.                                                                                                     |  |

| Arithmetic                        | PSUBS [B, W]            | Subtract with saturation.                                                                                                     |  |

| Antimiete                         | PSUBUS [B, W]           | Subtract unsigned with saturation.                                                                                            |  |

|                                   | PMULHW                  | Parallel multiply of four signed 16-bit words, with high-order 16 bits of 32-bit result chosen.                               |  |

|                                   | PMULLW                  | Parallel multiply of four signed 16-bit words, with low-order 16 bits of 32-bit result chosen.                                |  |

|                                   | PMADDWD                 | Parallel multiply of four signed 16-bit words; add together adjacent pairs of 32-bit results.                                 |  |

| Comparison                        | PCMPEQ [B, W, D]        | Parallel compare for equality; result is mask of 1s if true or 0s in false.                                                   |  |

|                                   | PCMPGT [B, W, D]        | Parallel compare for greater than; result is mask of 1s if true or 0s if false.                                               |  |

| 1                                 | PACKUSWB                | Pack words into bytes with unsigned saturation.                                                                               |  |

| de en la decretaga yez            | PACKSS [WB, DW]         | Pack words into bytes, or doublewords into words, with signed saturation.                                                     |  |

| Conversion                        | PUNPCKH [BW,<br>WD, DQ] | Parallel unpack (interleaved merge) high-order bytes, words, or doublewords from MMX register.                                |  |

|                                   | PUNPCKL [BW,<br>WD, DQ] | Parallel unpack (interleaved merge) low-order bytes, words, or doublewords from MMX register.                                 |  |

|                                   | PAND                    | 64-bit bitwise logical AND                                                                                                    |  |

| Logical                           | PNDN                    | 64-bit bitwise logical AND NOT                                                                                                |  |

|                                   | POR                     | 64-bit bitwise logical OR                                                                                                     |  |

| grading.Se                        | PXOR                    | 64-bit bitwise logical XOR                                                                                                    |  |

|                                   | PSLL [W, D, Q]          | Parallel logical left shift of packed words, doublewords, or quadword by amount specified in MMX register or immediate value. |  |

| Shift of will fold the            | PSRL [W, D, Q]          | Parallel logical right shift of packed words, doublewords, or quadword.                                                       |  |

|                                   | PSRA [W,D]              | Parallel arithmetic right shift of packed words, doublewords, or quadword.                                                    |  |

| Data Transfer                     | MOV [D, Q]              | Move doubleword or quadword to/from MMX register.                                                                             |  |

| State Mgt                         | EMMS                    | Empty MMX state (empty FP registers tag bits).                                                                                |  |

Note: If an instruction supports multiple data types [byte (B), word (W), doubleword (D), quadword (Q)], the data types are indicated in brackets.

instruction performs a left logical shift separately on each of the four words in the packed word operand; the PADDB instruction takes packed byte operands as input and performs parallel additions on each byte position independently to produce a packed byte output.

One unusual feature of the new instruction set is the introduction of saturation arithmetic. With ordinary unsigned arithmetic, when an operation overflows (i.e., a carry out of the most significant bit), the extra bit is truncated. This is referred to as wraparound, because the effect of the truncation can be, for example, to produce an addition result that is smaller than the two input operands. Consider the addition of the two words, in hexadecimal, F000h and 3000h. The sum would be expressed as

```

F000h = 1111\ 0000\ 0000\ 0000

+3000h = 0011\ 0000\ 0000\ 0000

10010\ 0000\ 0000\ 0000 = 2000h

```

If the two numbers represented image intensity, then the result of the addition is to make the combination of two dark shades turn out to be lighter. This is typically not what is intended. With saturation arithmetic, if addition results in overflow or subtraction results in underflow, the result is set to the largest or smallest value representable. For the preceding example, with saturation arithmetic, we have

```

F000h = 1111\ 0000\ 0000\ 0000

+3000h = 0011\ 0000\ 0000\ 0000

10010 0000 0000 0000

1111 1111 1111 1111 = FFFFh

```

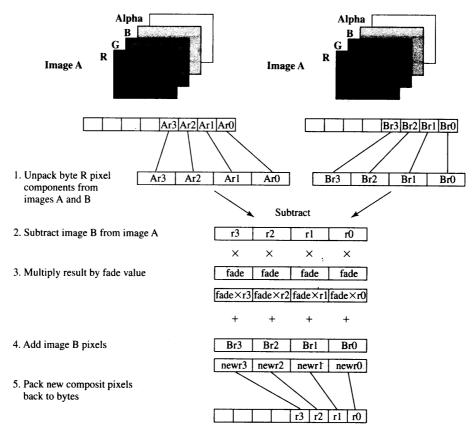

To provide a feel for the use of MMX instructions, we look at an example, taken from [PELE97]. A common video application is the fade-out, fade-in effect, in which one scene gradually dissolves into another. Two images are combined with a weighted average:

```

Result pixel = A pixel \times fade + B pixel \times (1 - fade)

```

This calculation is performed on each pixel position in A and B. If a series of video frames is produced while gradually changing the fade value from 1 to 0 (scaled appropriately for an 8-bit integer), the result is to fade from image A to image B.

Figure 10.10 shows the sequence of steps required for one set of pixels. The 8-bit pixel components are converted to 16-bit elements to accommodate the MMX 16-bit multiply capability. If these images use  $640 \times 480$  resolution, and the dissolve technique uses all 255 possible values of the fade value, then the total number of instructions executed using MMX is 535 million. The same calculation, performed without the MMX instructions, requires 1.4 billion instructions [INTE98].

# PowerPC Operation Types

The PowerPC provides a large collection of operation types. Table 10.12 lists the types and gives examples of each. Several features are worth noting.

Branch-Oriented Instructions The PowerPC supports the usual unconditional and conditional branch capabilities. Conditional branch instructions test a single bit of the condition register for true, false, or don't care and the contents of the count register for zero, nonzero, or don't care. Thus, there are nine separate conditions that can be

MMX code sequence performing this operation:

```

mm7, mm7

pxor

;zero out mm7

movq

mm3, fad val

;load fade value replicated 4 times

movd

mm0, imageA

;load 4 red pixel components from image A

movd

mm1, imageB

;load 4 red pixel components from image B

punpckblw

mm0, mm7

;unpack 4 pixels to 16 bits

unpack 4 pixels to 16 bits

punpckblw mm1, mm7

psubw

mm0, mm1

;subtract image B from image A

pmulhw

mm0, mm3

;multiply the subtract result by fade values

padddw

mm0, mm1

;add result to image B

packuswb

mm0, mm7

;pack 16-bit results back to bytes

```

Figure 10.10 Image Compositing on Color Plane Representation [PELE97]

defined for the conditional branch instruction. If the count register is tested for zero or nonzero, then it is decremented by 1 prior to the test. This is convenient for setting up iteration loops.

Branch instructions can also indicate that the address of the location following the branch is to be placed in the link register, described in Chapter 14. This facilitates call/return processing.

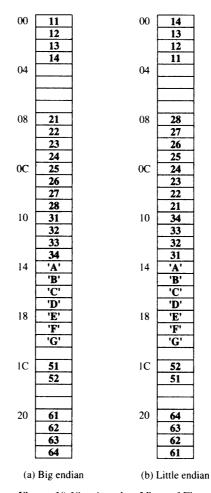

Load/Store Instructions In the PowerPC architecture, only load and store instructions access memory locations; arithmetic and logical instructions are performed

Table 10.12

PowerPC Operation Types (with Examples of Typical Operations)

| Instruction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | Branch-Oriented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ъ           | Unconditional branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| bl .        | Branch to target address and place effective address of instruction following the branch into the Link Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |